En aquest article passarem pel multiplexor, primer definirem què és un multiplexor després passarem pels seus tipus que són 2×1 i 4×1, després passarem per la Implementació del 2×1 mux i superior. mux amb mux d'ordre inferior, per fi conclourem el nostre article amb algunes aplicacions, avantatges i algunes preguntes freqüents.

Taula de contingut

- Què són els multiplexadors?

- Tipus de Mux

- Multiplexor 2×1

- Multiplexor 4×1

- Implementació de diferents portes amb 2:1 Mux

- Implementació de MUX d'ordre superior mitjançant MUX d'ordre inferior

- Avantatges i desavantatges de MUX

Què són els multiplexadors?

Un multiplexor és a circuit combinacional que té moltes entrades de dades i una única sortida, depenent de les entrades de control o de selecció. Per a N línies d'entrada, calen línies de selecció log2(N), o de manera equivalent, per

Multiplexor

Tipus de Mux

El Mux pot ser de diferents tipus segons l'entrada, però en aquest article passarem per dos tipus principals de mux que són

- 2×1 Mux

- 4×1 Mux

Multiplexor 2×1

El 2×1 és un circuit fonamental que també es coneix com a multiplexor 2 a 1 que s'utilitzen per triar-ne un senyal de dues entrades i la transmet a la sortida. El mux 2×1 té dues línies d'entrada, una de sortida i una única línia de selecció. Té diverses aplicacions en sistemes digitals com en microprocessador s'utilitza per seleccionar entre dues fonts de dades diferents o entre dues instruccions diferents.

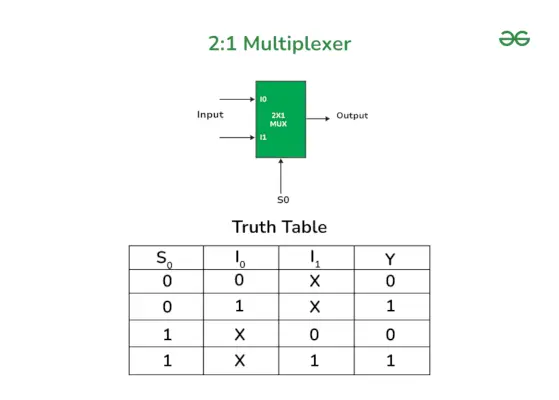

Diagrama de blocs del multiplexor 2:1 amb taula de veritat

A continuació es mostra el diagrama de blocs i la taula de veritat de 2:1 Mux. En aquest diagrama de blocs on I0 i I1 són les línies d'entrada, Y és la línia de sortida i S0 és una única línia de selecció.

Diagrama de blocs del multiplexor 2:1 amb taula de veritat

La sortida del 2×1 Mux dependrà de la línia de selecció S0,

- Quan S és 0 (baix), se selecciona I0

- quan S0 és 1 (Alt), se selecciona I1

Expressió lògica de 2×1 Mux

Utilitzant la taula de veritat, l'expressió lògica de Mux es pot determinar com

Y=overline{S_0}.I_0+S_0.I_1

Esquema de circuits de multiplexadors 2×1

Utilitzant la taula de veritat circuit el diagrama es pot donar com a

Diagrama de circuit de 2×1 Mux

Multiplexor 4×1

El multiplexor 4×1 que també es coneix com el multiplexor 4 a 1. És un multiplexor que té 4 entrades i una única sortida. La sortida es selecciona com una de les 4 entrades que es basa en les entrades de selecció. El nombre de línies de selecció dependrà del nombre de l'entrada determinat per l'equació

Diagrama de blocs del multiplexor 4×1

Al diagrama de blocs donat, I0, I1, I2 i I3 són les 4 entrades i Y és la sortida única que es basa en les línies de selecció S0 i S1.

La sortida del multiplexor està determinada pel valor binari de les línies de selecció

- Quan S1S0=00, es selecciona l'entrada I0.

- Quan S1S0=01, es selecciona l'entrada I1.

- Quan S1S0=10, es selecciona l'entrada I2.

- Quan S1S0=11, es selecciona l'entrada I3.

Taula de veritat del multiplexor 4×1

A continuació es mostra el Taula de la Veritat de multiplexador 4×1

1.000 milions a milions

Esquema de circuits de multiplexadors 4×1

Utilitzant la taula de veritat el diagrama de circuits es pot donar com

El multiplexor pot actuar com a circuit combinacional universal. Totes les portes lògiques estàndard es poden implementar amb multiplexors.

Implementació de diferents portes amb 2:1 Mux

A continuació es mostren la implementació de la porta diferent amb 2:1 Mux

Implementació de la porta NOT utilitzant 2: 1 Mux

La porta Not de 2:1 Mux es pot obtenir mitjançant

- Connecteu el senyal d'entrada a una de les línies d'entrada de dades (I0).

- A continuació, connecteu una línia (0 o 1) a l'altra línia d'entrada de dades (I1)

- Connecteu la mateixa línia d'entrada Seleccioneu la línia S0 que està connectada a D0.

A continuació es mostra el diagrama per a la representació lògica de NO porta utilitzant 2: 1 Mux

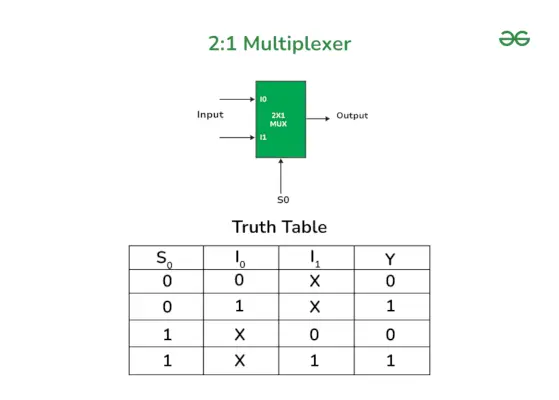

Implementació de la porta AND utilitzant 2: 1 Mux

La porta I de 2:1 Mux es pot obtenir mitjançant

- Connecteu l'entrada Y a I1.

- Connecteu l'entrada X a la línia de selecció S0.

- Connecteu una línia (0) a I0.

A continuació es mostra el diagrama per a la representació lògica de I porta utilitzant 2: 1 Mux

Per a més informació sobre el Implementació de la porta AND utilitzant 2: 1 Mux

Implementació de la porta OR amb 2: 1 Mux

La porta OR de 2:1 Mux es pot obtenir mitjançant

- Connecteu l'entrada X a la línia de selecció S0.

- Connecteu l'entrada Y a I1.

- Connecteu la línia (1) a I1.

A continuació es mostra el diagrama per a la representació lògica de O porta utilitzant 2: 1 Mux

La implementació de portes NAND, NOR, XOR i XNOR requereix dos Mux 2:1. El primer multiplexor actuarà com a porta NO que proporcionarà una entrada complementada al segon multiplexor.

Implementació de la porta NAND utilitzant 2: 1 Mux

La porta NAND de 2:1 Mux es pot obtenir mitjançant

- En el primer mux prenem les entrades i 1 i 0 i y com a línia de selecció.

- En segon MUX, la sortida de mux està connectada a I1.

- la línia (1) es dóna a la I0.

- x es dóna com a línia de selecció per al segon Mux.

A continuació es mostra el diagrama per a la representació lògica de Porta NAND utilitzant 2: 1 Mux

Per a més informació sobre el Implementació de la porta NAND utilitzant 2: 1 Mux

Implementació de la porta NOR utilitzant 2: 1 Mux

La porta Nor de 2:1 Mux es pot obtenir mitjançant

- En el primer mux prenem les entrades i 1 i 0 i y com a línia de selecció.

- En segon MUX, la sortida de mux està connectada a I0.

- la línia (0) es dóna a la I1.

- x es dóna com a línia de selecció per al segon Mux.

A continuació es mostra el diagrama per a la representació lògica de porta NOR utilitzant 2: 1 Mux

Per a més informació sobre el Implementació de la porta NOR utilitzant 2: 1 Mux

Implementació de la porta EX-OR utilitzant 2: 1 Mux

La porta Nor de 2:1 Mux es pot obtenir mitjançant

- En el primer mux prenem les entrades i 1 i 0 i y com a línia de selecció.

- En segon MUX, la sortida de mux està connectada a I1.

- y es dóna a l'I0.

- x es dóna com a línia de selecció per al segon Mux.

A continuació es mostra el diagrama per a la representació lògica de Porta EX-OR utilitzant 2: 1 Mux

ordres sql ddl

Implementació de la porta EX-NOR utilitzant 2: 1 Mux

A continuació es mostra el diagrama per a la representació lògica de Porta EX-OR utilitzant 2: 1 Mux

La porta Nor de 2:1 Mux es pot obtenir mitjançant

- En el primer mux prenem les entrades i 1 i 0 i y com a línia de selecció.

- En segon MUX, la sortida de mux està connectada a I0.

- y es dóna a la I1.

- x es dóna com a línia de selecció per al segon Mux.

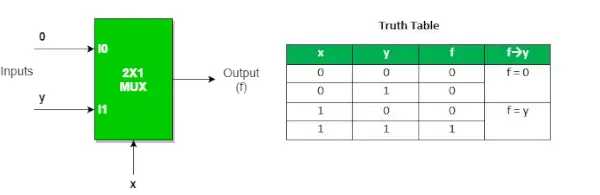

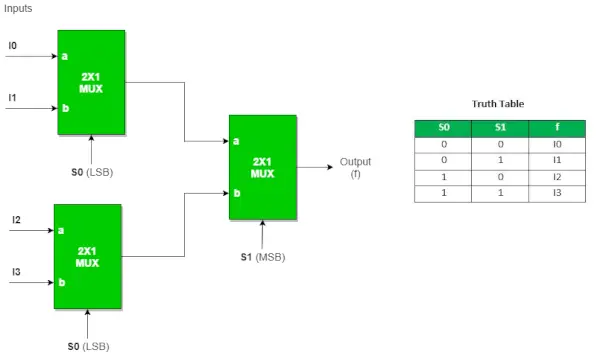

Implementació de MUX d'ordre superior mitjançant MUX d'ordre inferior

A continuació es mostra la implementació de MUX d'ordre superior mitjançant MUX d'ordre inferior

4: 1 MUX amb 2: 1 MUX

Es requereixen tres 2: 1 MUX per implementar 4: 1 MUX.

De la mateixa manera,

Mentre que un MUX 8:1 requereix set (7) MUX 2:1, un MUX 16:1 requereix quinze (15) MUX 2:1 i un MUX 64:1 requereix seixanta-tres (63) MUX 2:1. Per tant, podem treure la conclusió que an

16: 1 MUX amb 4: 1 MUX

A continuació es mostra el diagrama lògic de 16:1 Mux amb 4:1 Mux

En general, per implementar B : 1 MUX amb A : 1 MUX , s'utilitza una fórmula per implementar el mateix.

B/A = K1,

K1/ A = K2,

K2/A = K3

KN-1/ A = KN= 1 (fins que obtenim 1 recompte de MUX).

I després sumeu tots els nombres de MUX = K1 + K2 + K3 + .... + KN.

Per implementar 64: 1 MUX mitjançant 4: 1 MUX

Amb la fórmula anterior, podem obtenir el mateix.

64/4 = 16

16/4 = 4

4/4 = 1 (fins que obtinguem 1 recompte de MUX)

Per tant, es requereix un nombre total de 4: 1 MUX per implementar 64: 1 MUX = 16 + 4 + 1 = 21.

f (A, B, C) =

utilitzant A i B com a línies de selecció per a 4: 1 MUX,

cadena java a char

AB com a selecció: Ampliant els minterms a la seva forma booleana i veureu el seu valor 0 o 1 al lloc Cth perquè es puguin col·locar d'aquesta manera.

AC com a seleccionat : s'expandeixen els minterms a la seva forma booleana i es veurà el seu valor 0 o 1 en Bth lloc perquè es puguin col·locar d'aquesta manera.

BC com a selecte : ampliant el minterms a la seva forma booleana i veurà el seu valor 0 o 1 a Athlloc perquè puguin ser col·locats d'aquesta manera.

Avantatges i desavantatges de MUX

A continuació es mostren els avantatges i desavantatges de MUX

Avantatges de MUX

A continuació es mostren els avantatges de MUX

- Eficiència : El Mux té una bona eficiència a l'hora d'encaminar diversos senyals d'entrada a un senyal de sortida únic basat en senyals de control.

- Optimització : El Mux ajuda a conservar recursos com ara cables, agulles i circuit integrat (I C).

- Implementació diferent: El Mux es pot utilitzar per implementar diferents funcions lògiques digitals com AND,OR, etc.

- Flexibilitat: Mux es pot configurar fàcilment segons els requisits i acomodar diferents fonts de dades, millorant la versatilitat del sistema.

Inconvenients de MUX

A continuació es mostren els desavantatges de MUX

- Nombre limitat de fonts de dades: El nombre d'entrada que pot prendre un multiplexor està restringit pel nombre de línies de control, la qual cosa pot causar limitacions en determinades aplicacions.

- Retard: Els multiplexadors poden tenir algun retard en el camí del senyal, cosa que pot tenir un impacte en el rendiment del circuit.

- Justificació del control complex: La lògica de control dels multiplexors pot ser complexa, especialment per als multiplexors més grans amb un gran nombre d'entrades.

- Ús d'energia: Els multiplexors poden consumir més energia en comparació amb altres l simples porta ògica , especialment quan tenen un gran nombre d'entrades.

Aplicacions de MUX

A continuació es mostren les aplicacions de MUX

- Encaminament de dades : El Mux s'utilitza per a l'encaminament de dades en el sistema digital on seleccionen una de les diverses línies de dades i la reencaminen a la sortida.

- Selecció de dades : El Mux s'utilitza per a la selecció de dades on seleccionen la font de dades segons les línies de selecció.

- Conversió d'analògic a digital : S'utilitzen els Mux ADC per seleccionar diferents canals d'entrada analògic.

- Descodificació d'adreces : S'utilitzen els Mux Microprocessadors o memòria per a la descodificació d'adreces.

- Implementació de la funció lògica : Els muxes es poden utilitzar per implementar diverses funcions lògiques.

Conclusió

En aquest article hem passat pel MUX, hem vist diferents tipus de Mux que són 2×1 i 4×1 Mux, hem passat per la implementació del 2×1 mux i superior amb mux d'ordre inferior. També hem passat pels seus avantatges, desavantatges i aplicacions en breu.

Multiplexors en lògica digital - Preguntes freqüents

Per què es considera complexa la lògica de control dels multiplexors?

El Mux pot ser complex, especialment per a multiplexors més grans a causa dels senyals de control que seleccionen les entrades en funció dels requisits de l'aplicació.

Quins són els diferents tipus d'arquitectures de multiplexor?

Les arquitectures Mux es canvien en funció de factors com el nombre total d'entrades, el nombre de línies de selecció i la lògica utilitzada per a la selecció d'entrada.

Com s'utilitzen les aplicacions de processament de senyal digital (DSP) els multiplexors?

A les aplicacions DSP, els multiplexors s'utilitzen per a l'encaminament, la selecció i el processament del senyal.